技術分享

EMC是什么?PCB設計中如何減少EMC?10個PCB設計技巧幫你減少EMC

發(fā)布時間:2023-07-16 00:00:00 瀏覽:1022次

依舊自我介紹,張工,NPI 工程師,如果還不知道我具體是干什么的,歡迎看我的第一篇文章(主頁點進去即可)。

萬變不離其宗,作為 NPI 工程師,DFM 可制造性分析涉及的范圍非常廣,今天主要是關于:EMC,PCB設計中如何降低EMC?

一、EMC是什么?

在PCB設計中,主要的EMC問題包括3種:傳導干擾、串擾干擾、輻射干擾。

1、傳導干擾

傳導干擾通過引線去耦和共模阻抗去耦影響其他電路,例如:噪聲通過電源電路進入系統(tǒng),支持電路將受到噪聲的影響。

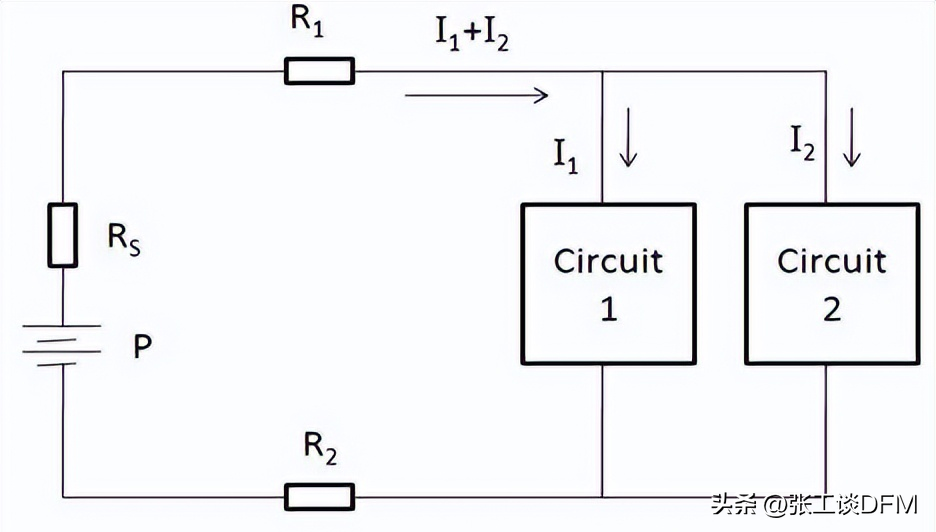

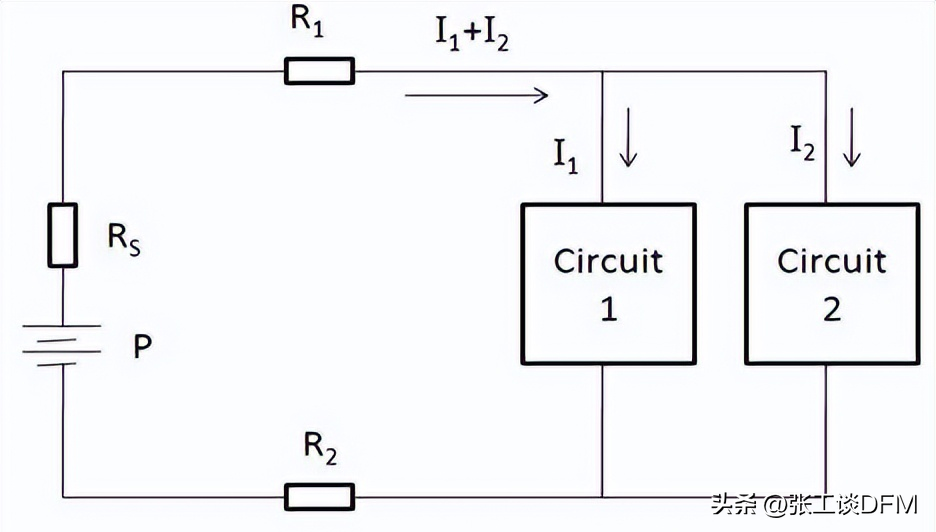

下圖顯示了通過共模阻抗進行的噪聲去耦。電路1和電路2通過同一根導線獲得電源電壓的和接地環(huán)路。如果其中一個電路的電壓突然需要提高,另一個電路將降低,因為公共電源和兩個回路之間的阻抗。

2、串擾干擾

串擾干擾是指一根信號線對相鄰信號線的干擾,通常發(fā)生在相鄰的電路和導體上,其特點是電路與導體之間存在互電容和互阻抗。例如:PCB上的帶狀線,信號電平較低,當平行線長度超過10cm時,串擾就會出現(xiàn)。

由于電場可以通過互電容引起串擾,磁場可以通過互阻抗引起串擾,因此首先要確認哪個去耦起到主要作用,是電場(互電容)去耦還是磁場(互阻抗)去耦。功率阻抗和接受器阻抗的乘積可以作為參考,取決于電路和頻率之間的配置。

3、輻射干擾

輻射干擾是指由自由電磁波釋放的輻射引起的干擾。PCB中的輻射干擾是指電纜和內部線路之間的共模輻射干擾。當電磁波照射在輸電路線上時,會出現(xiàn)電場對線路的解耦問題,線路上分布的小電壓源分為CM(共模)和DM(差模)。CM電流是指來自兩根導聯(lián)的電流幾乎相等的幅度和相同的相位。而DM電流是指來自兩根導聯(lián)的電流具有相同的輻射和相反的相位。

二、如何減少EMC問題的產生?

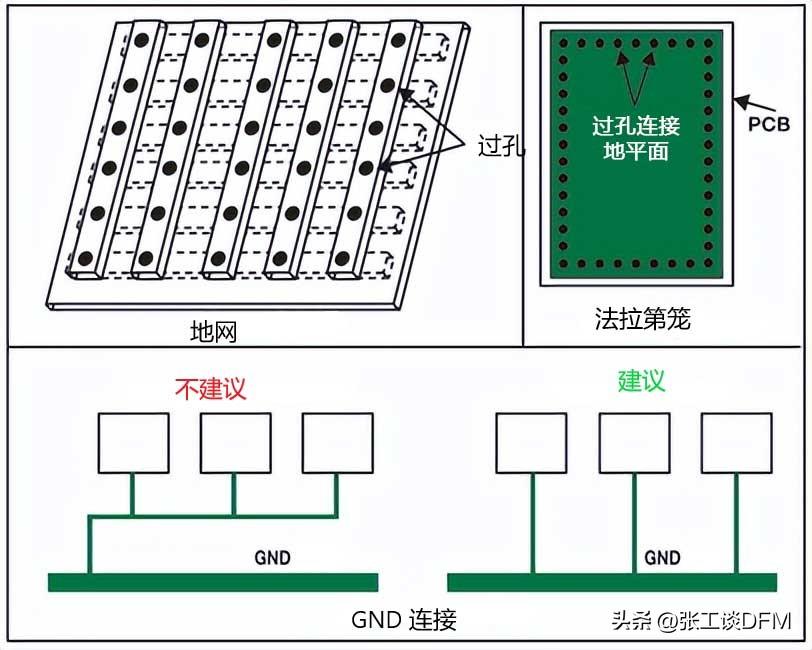

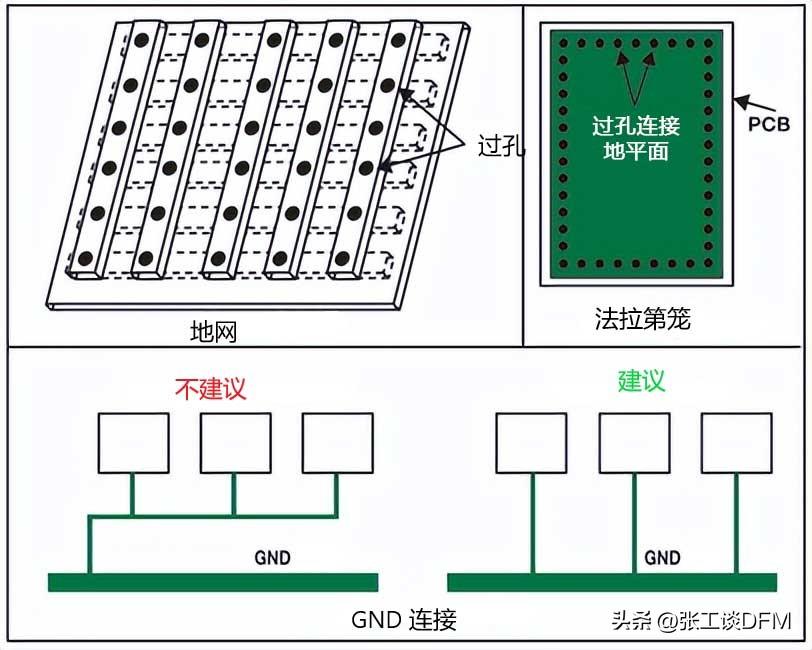

1、低電感接地系統(tǒng)

在PCB設計中最常用的就是低電感接地系統(tǒng)。最大化PCB上的接地面積可以降低系統(tǒng)中的接地電感,這樣可以減少電磁輻射和干擾,可以使用不同的方法將信號接地。

在PCB設計中,最好的方法是將PCB中其中一層接地,這樣可以提供低阻抗,如果不能整層接地,就采用接地網(wǎng),在這種情況下,接地電感取決于網(wǎng)格之間的空間。

低電感接地系統(tǒng)

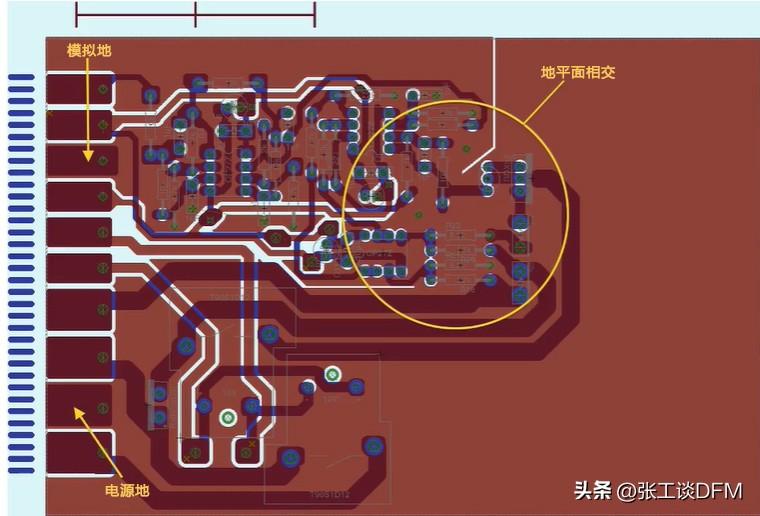

下圖為各種地平面應用圖,高速電路靠近地放置、低速電路靠近電源層。銅填充區(qū)域始終接地。否則,可能會充當天線并導致EMC問題。在電路中需要多個電源的情況下,將電源層和接地層分開可以防止電源彼此產生噪聲。

各種地平面應用圖

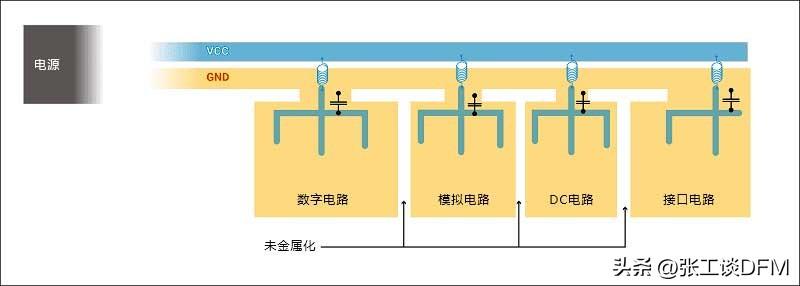

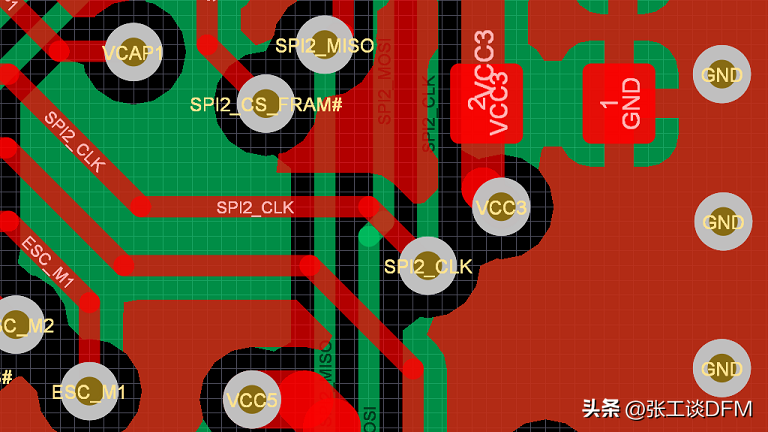

2、元器件根據(jù)功能進行放置

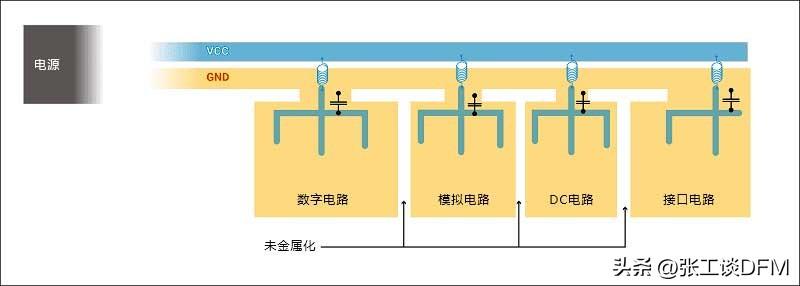

PCB上的組件應該根據(jù)功能進行分組。例如模擬、數(shù)字、電源、低速電路、高速電路。每個組件的信號走線必須保持在定義的區(qū)域內。當信號需要從一個子系統(tǒng)連接到另一個子系統(tǒng)的時候,可以使用濾波器。

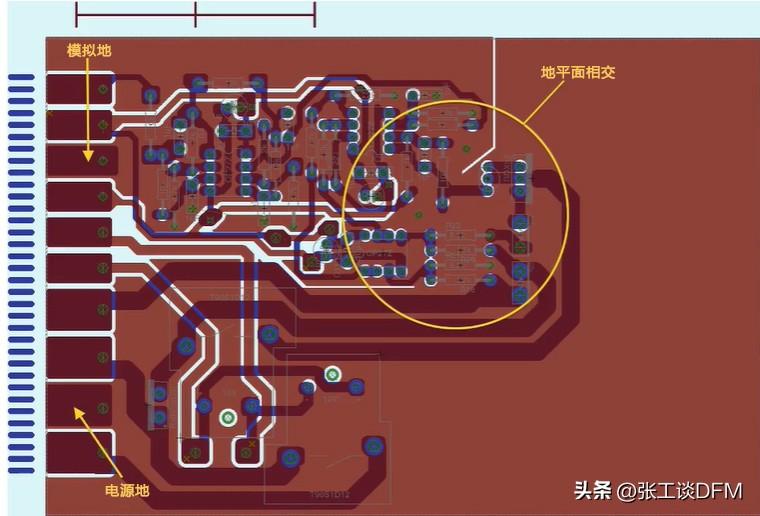

下圖說明了如何使用分段將四個不同的電路分開。地平面使用未金屬化的護城河/通道有效地隔離了電路。電感和電容對每個電路進行濾波,電源層之間的耦合減少。

元器件根據(jù)功能進行放置

3、PCB層數(shù)排列

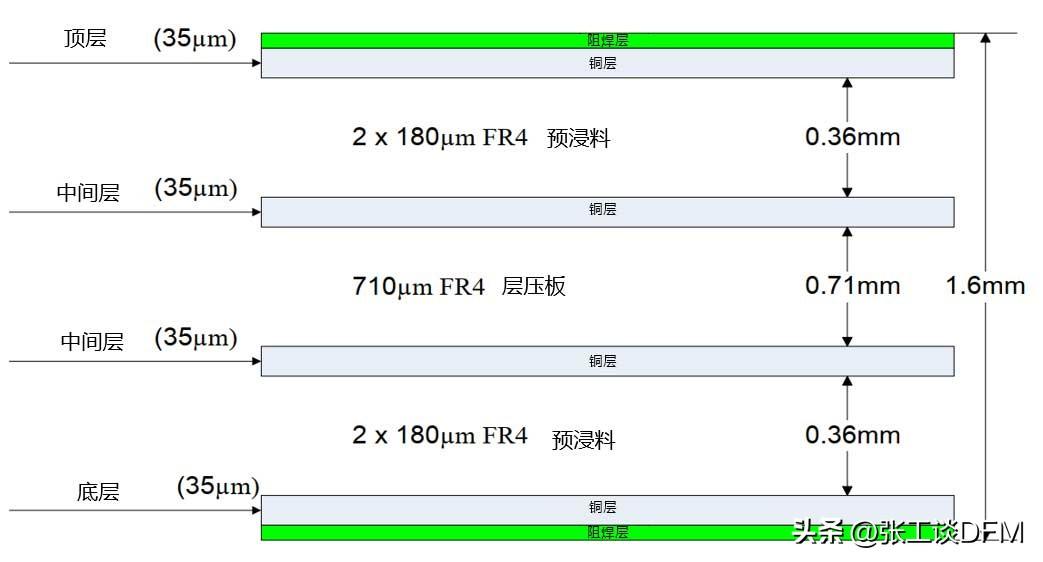

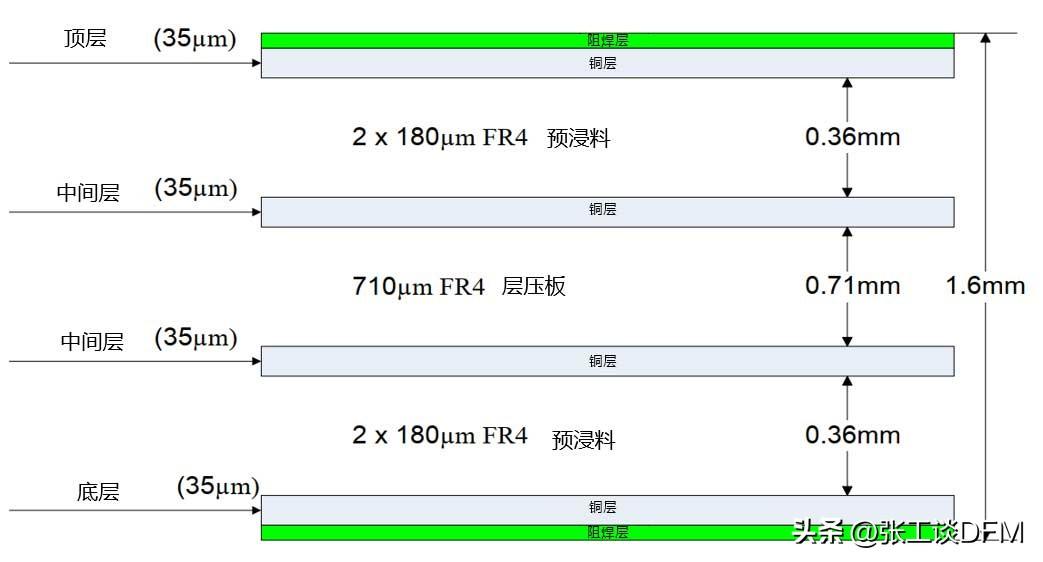

PCB 的 EMC 性能還取決于其層的排列。在 2 層 PCB 的情況下,應將整個層用作接地層。如果不可能整層接地,則應放置接地網(wǎng)。對于 4 層 PCB,接地層以下的層應作為電源層 。超過 4 層的 PCB 應具有偶數(shù)層,并由交替的接地層和信號層組成,以避免出現(xiàn) EMC 問題。

下圖顯示了圍繞核心(層壓板)構建的 FR4 1.6 毫米 4 層 PCB 的疊層。核心是兩面都有銅層的厚介電片。核心的頂部和下方添加了薄的預浸料,即介電材料片。對于這種特定情況,中間層 1 和 2 分別代表接地層和電源層。頂層和底層用作信號平面,每側可以焊接多個組件。多層堆疊的配置在 EMC 應用中起著至關重要的作用。

PCB 層堆疊

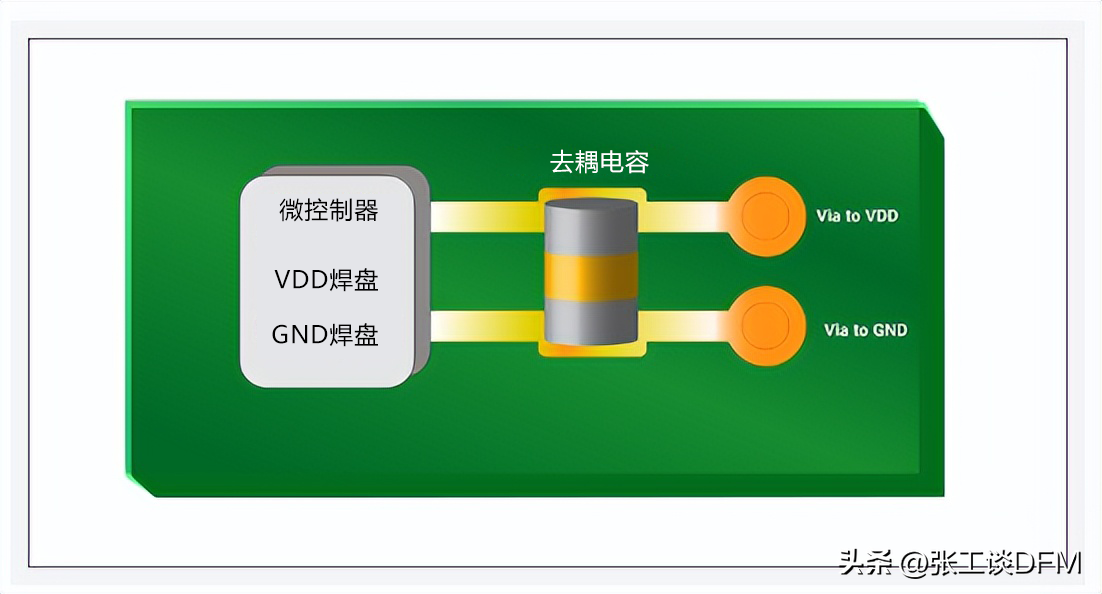

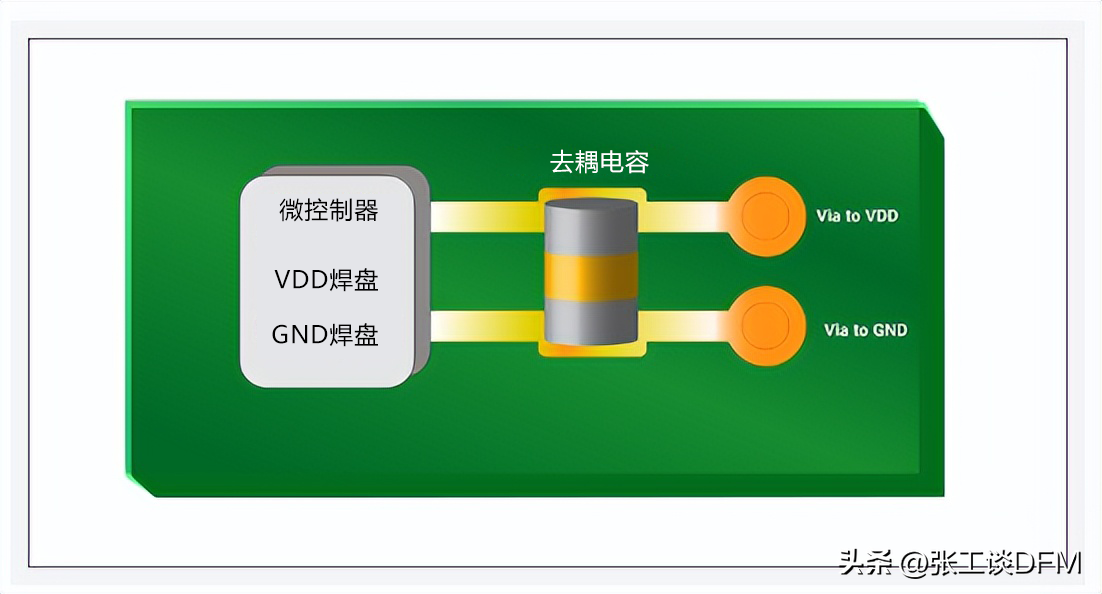

4、添加去耦電容

當 IC 工作時,由于其內部結構,它們會以高頻進行切換。這種情況會在 IC 連接軌道中產生開關噪聲。如果不控制這種噪聲,它將導致發(fā)射,從而導致 EMI 。通過在 IC 附近放置一個去耦電容,可以減少 PCB 上開關噪聲的傳播并將噪聲引導至地面。

去耦電容布局

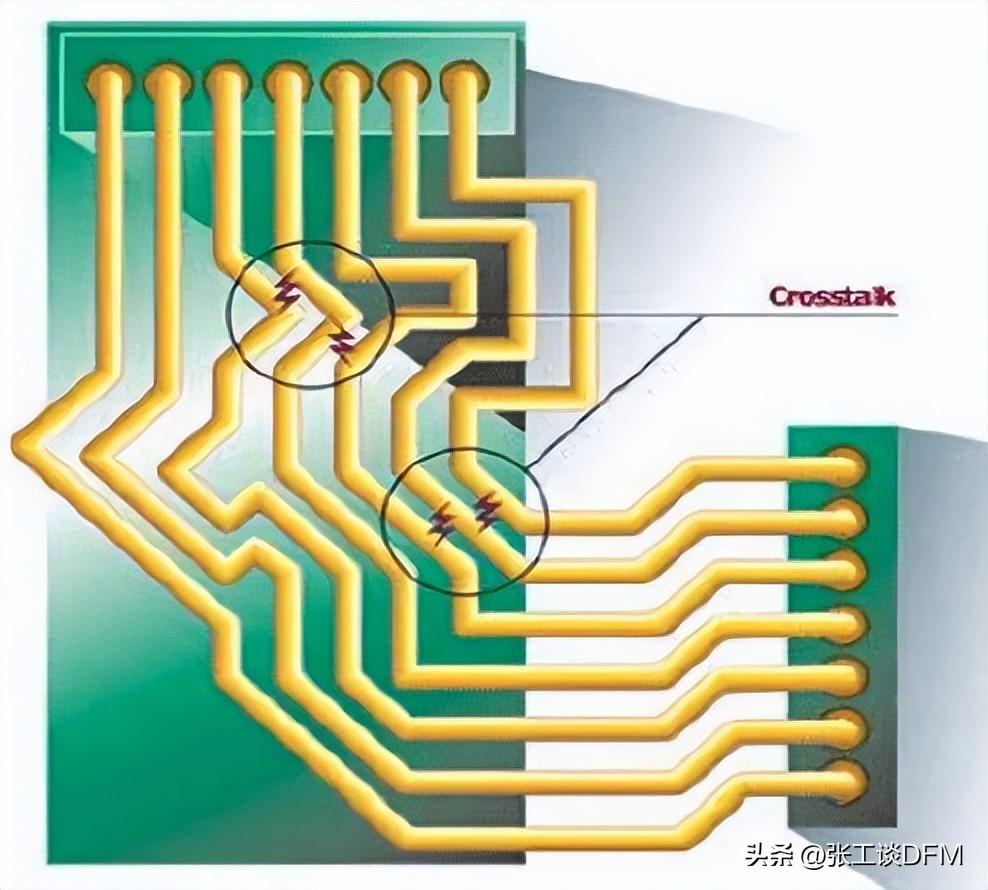

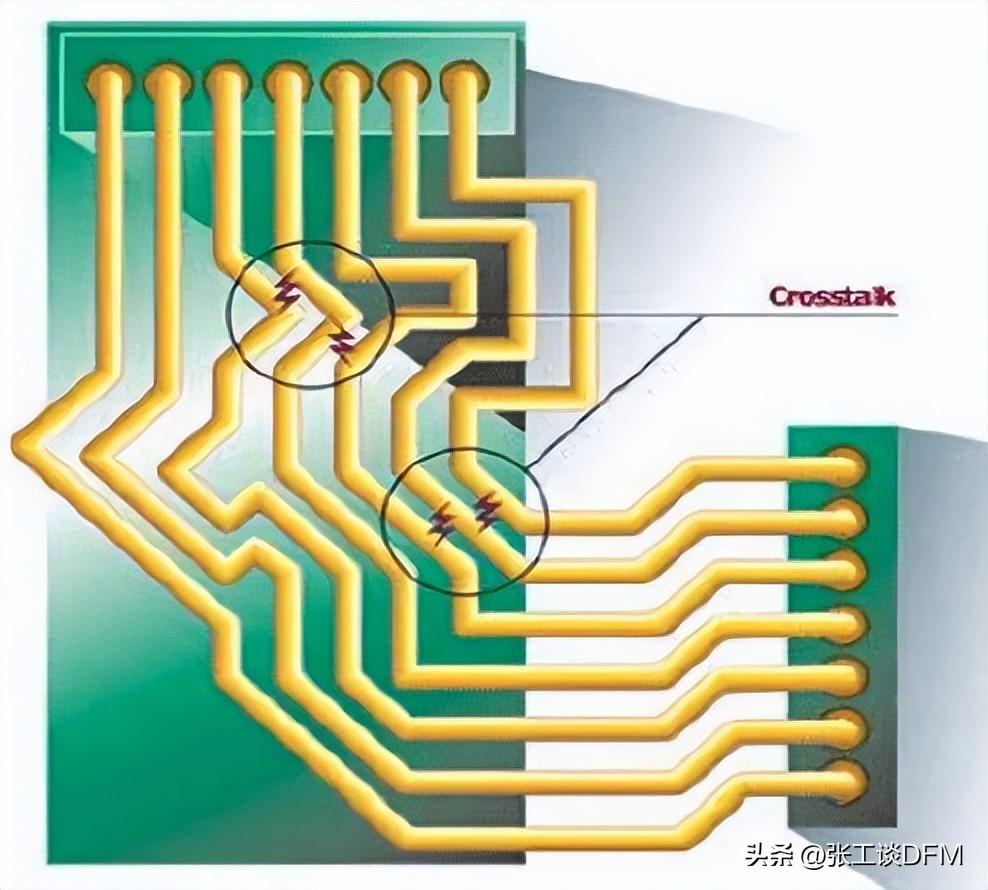

5、避免串擾

串擾用于識別由 PCB 上的一條軌道到附近另一條軌道的電磁噪聲引起的干擾。PCB 中的串擾通常發(fā)生在同一層中并排的軌道或相鄰層中的一個軌道上。這種情況表現(xiàn)為噪聲,如果振幅過大可能會導致故障 。

串擾示例

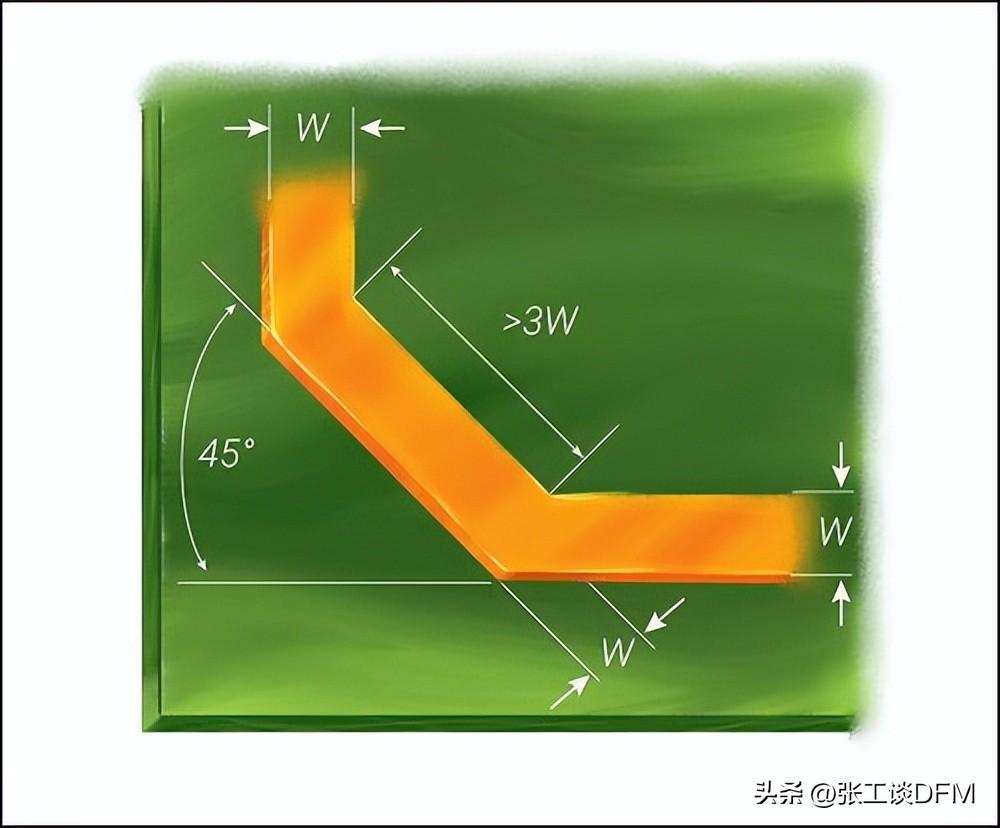

6、不要90°走線

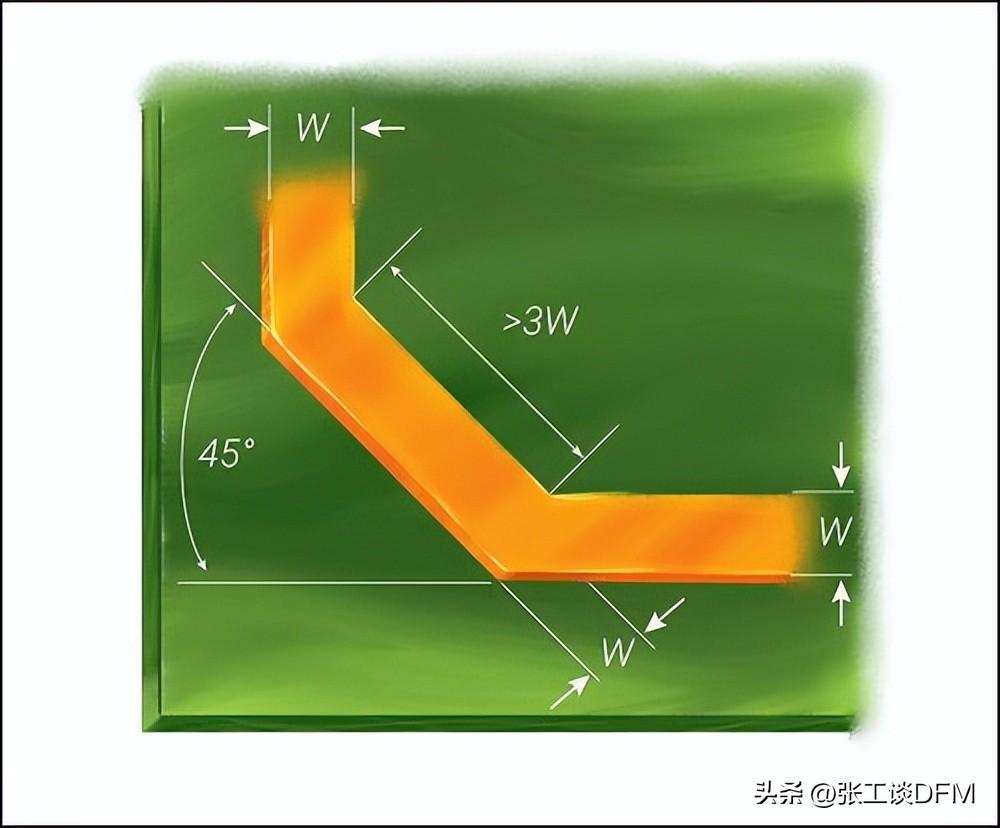

與過孔類似,不應實施直角 90° 軌道轉彎,因為它會增加寄生電容,導致特性阻抗發(fā)生變化,從而導致反射。如圖 所示,所有正交走線都應采用 45° 彎曲,以限制耦合到附近走線的噪聲。

45°走線

45° 角跡線,其中 W 是跡線寬度

信號走線的寬度從源到負載應該是恒定的。改變跡線的寬度會產生阻抗變化(電阻、電感和電容),因此在高速信號和線路阻抗不平衡的情況下會引起反射。此外,應盡量減少電源和接地平面中的分離孔徑(即寬過孔或長孔),因為它們會在平面內產生不均勻區(qū)域。這會導致屏蔽效能降低和總阻抗增加 。

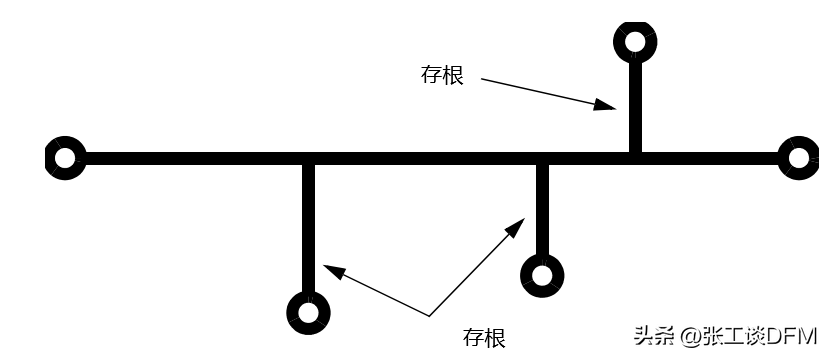

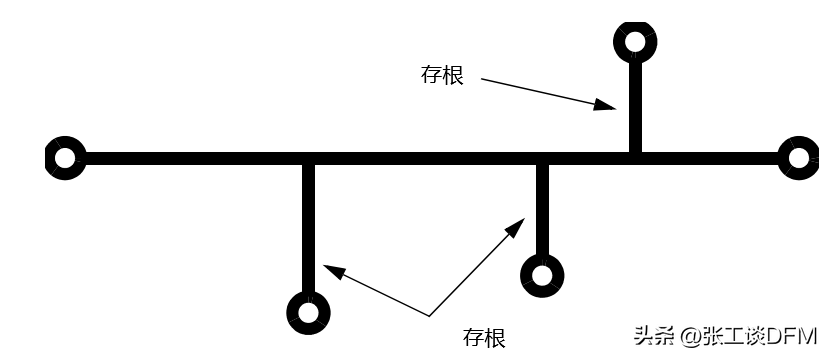

存根走線

短截線會產生反射,并有可能將波長可分天線添加到電路中。盡管短截線長度可能是系統(tǒng)中任何已知信號的非四分之一波長整數(shù),但入射的輻射 EM 波可能會在短截線上產生共振。因此,在布線時應避免帶有承載高頻或敏感信號的走線的存根 。

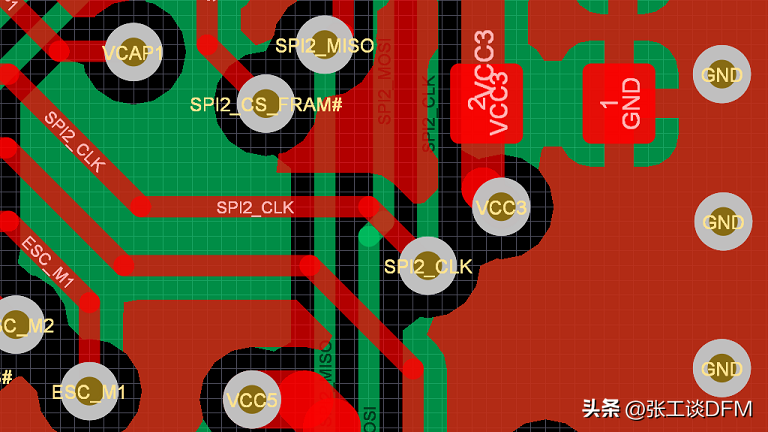

7、走線分離

走線分離可最大限度地減少相同或不同 PCB 層上相鄰/平行跡線之間的串擾和電磁耦合。一般規(guī)則規(guī)定走線之間的間隔(在中心到中心之間測量)應大于或等于 3 x 走線寬度。間隔越大,串擾和耦合越低。

走線分離

通常在同一層走線的所有走線都是微帶線。那是放置在地平面頂部的平面?zhèn)鬏斁€。它們可以傳輸從直流到高頻的信號。對于在 PCB 的同一層上需要更多并行跡線且間距最小的特定情況,可以使用共面波導 (CPW)。例如,與微帶線相比,接地的 CPW 通過將接地平面放置在電介質材料的底部和同一平面上來增加電路周圍的接地量,確保接地平面在信號傳輸線的兩側連續(xù)延伸。它可以最大限度地減少 PCB 不同層上信號走線之間的串擾。

8、過孔遠離關鍵信號走線

過孔在多層 PCB 中用于信號路由。如果設計不當,一些過孔會引入寄生電容和電感效應。應避免此類過孔并將其放置在離關鍵走線盡可能遠的地方。由于過孔中的寄生電容和電感,過孔和跡線之間存在阻抗不匹配,從而產生反射。當無法避免過孔時,應確保接地過孔靠近信號過孔放置。這種布置減少了特性阻抗值的變化,從而減少了反射。

9、走線附近放置一個參考平面

更重要的是在走線附近放置一個參考平面以防止輻射 EMI。這適用于全數(shù)字系統(tǒng)和混合信號系統(tǒng),兩者都應使用參考平面層,并且不應在參考導體不連續(xù)或完全沒有參考導體的區(qū)域上布線。

走線附近放置一個參考平面

PCB 疊層中的阻抗計算器可以計算出接地間隙。然而,高速信號應該在統(tǒng)一的平面上布線,以確保有清晰的返回路徑。

對于阻抗控制系統(tǒng),提供隔離的正確方法是除了在 PCB 疊層中放置參考層之外,還使用共面布置的接地灌注。通常,該過程是通過比較沒有接地的跡線與同一疊層和層中的共面跡線的阻抗來查看附近的導體如何改變跡線的阻抗。如果接地點太近,分布寄生電容會與線路的分布自電容并聯(lián),因此阻抗會降低。

10、模擬信號遠離高速信號或者開關信號

承載模擬信號的軌道應遠離高速或開關信號,并應始終受到接地信號的保護。低通濾波器可用于避免模擬軌道周圍的高頻噪聲。此外,重要的是模擬和數(shù)字子系統(tǒng)的地平面不要共用 。