模擬IP集成中的常見芯片問題

發(fā)布日期:2023-11-07

點擊次數(shù):606

盡管過去十年人們擔(dān)心摩爾定律終會走到盡頭,但微電子行業(yè)通過持續(xù)的創(chuàng)新和創(chuàng)造力,繼續(xù)適應(yīng)新的物理約束和產(chǎn)品要求。大部分創(chuàng)意能量都投入到了模擬、射頻和混合信號模塊作為嵌入式 IP 的開發(fā)中。

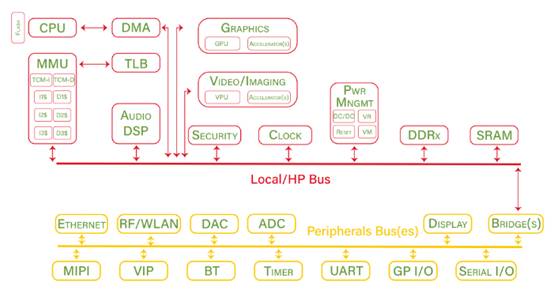

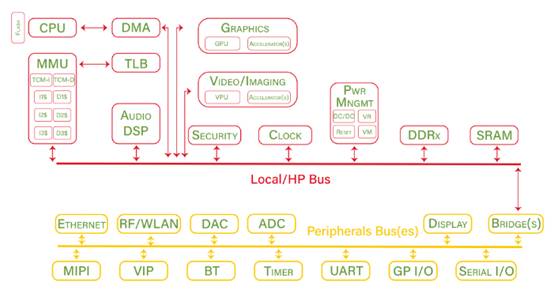

圖 1該框圖突出顯示了多媒體 SoC 設(shè)計。P2F Semi

現(xiàn)在可用的模擬/射頻/混合信號 IP 的選擇既廣泛又深入。人們可以在以下主要類別中找到大量 7 nm(有時甚至是 5 nm)的硬件模塊:

PLL 和 DLL:提供多種速度、抖動和功率規(guī)格

DAC 和 ADC:分辨率為 8 位至 24 位,速率高達 300 MSPS

PHY 和 SerDes:針對廣泛的市場選擇,例如無線(Wi-Fi 和 5G)、網(wǎng)絡(luò)(LAN、WAN 和存儲)、計算(USB、PCIe、MIPI)和內(nèi)存(DDR,包括 G 和 LP 變體,以及 HBM 和許多其他)

可以組裝更小的組件來創(chuàng)建個性化模擬前端 (AFE)、電源管理功能和射頻模塊

該行業(yè)不斷取得工藝技術(shù)進步,以支持對更高門數(shù)、更低功耗、更高性能和更多功能的永無止境的需求。其中包括三阱隔離、絕緣體上硅、P+ 保護環(huán)、FinFET 和溝槽隔離。其中許多功能促進了我們今天看到的模擬、射頻和混合信號 IP 的激增。這些基板的添加還減少了設(shè)計人員在超深亞微米領(lǐng)域一直面臨的一些復(fù)雜問題的嚴(yán)重程度,例如隱藏在轉(zhuǎn)換速率中的模擬噪聲源、阻抗匹配和端接復(fù)雜性以及支持巨大帶寬的電路。

然而,面對 16 nm 及以下 SoC 設(shè)計中與模擬電路并排放置的大量門數(shù),即使是新穎的工藝增強也顯得不足。事實上,與模擬/射頻宏非常接近的大型高性能數(shù)字模塊帶來的信號和電源完整性挑戰(zhàn)正在從芯片擴展到封裝和 PCB,而這兩者都在努力跟上硅技術(shù)進步的步伐。SoC 設(shè)計人員越來越發(fā)現(xiàn)自己被迫將工作范圍擴大到其他兩個領(lǐng)域,以確保他們的芯片設(shè)計能夠按預(yù)期運行。

這個由多部分組成的文章系列探討了嵌入式模擬和 RF IP 核如何對芯片、封裝和 PCB 功能產(chǎn)生負面影響,其影響是多種多樣的。我們還將討論如何在所有三個層面上防范這些問題,以及這些解決方案如何相輔相成。

硅實踐

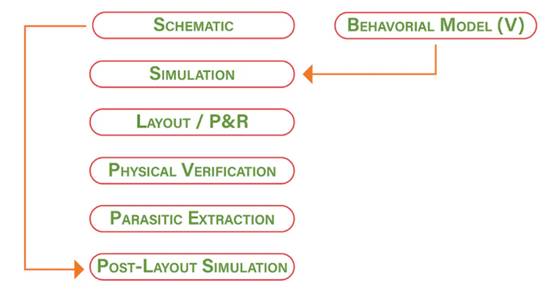

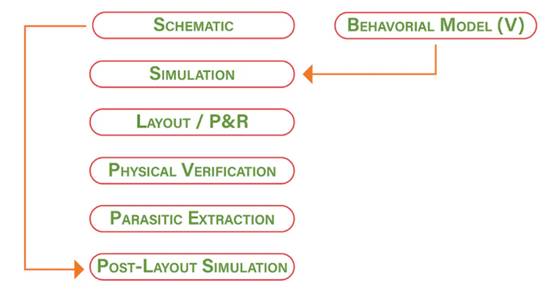

在過去的二十年里,為模擬和數(shù)字電路設(shè)計創(chuàng)建統(tǒng)一的工具和方法流程的嘗試迄今為止已被證明是徒勞的。然而,人們對模擬流程的基本輪廓達成了普遍共識,如圖2所示。

圖 2顯示基本模擬設(shè)計流程的視圖。P2F Semi

盡管流程看起來相當(dāng)簡單,但細節(jié)決定成敗。

模擬電路對電路的布局和布線方式非常敏感。設(shè)計規(guī)則(走線和通孔間距、差分信號和額外接地引腳)有助于避免或至少減少導(dǎo)致 EMI 問題的基板耦合和鄰近效應(yīng)。這就是為什么設(shè)計規(guī)則檢查 (DRC) 是布局后物理驗證工作的一部分。布局與原理圖 (LVS) 檢查也是驗證預(yù)期連接性的同一步驟的一部分。

寄生參數(shù)提取直接影響潛在耦合源的識別,寄生參數(shù)的反向注釋通常會導(dǎo)致原理圖和布局的變化。不幸的是,這將影響時序、動態(tài)范圍、負載、增益和功率,并產(chǎn)生一組全新的寄生效應(yīng)。因此,返回設(shè)計流程開始的迭代循環(huán)是一種悲劇性的必然,這就是為什么模擬設(shè)計被認為更像是一門藝術(shù)而不是一門科學(xué)。

模擬塊的集成

因此,將終的模擬模塊集成到整個 ASIC/SoC 設(shè)計中會帶來一系列全新的問題。對于數(shù)字和模擬電路模塊,芯片布局規(guī)劃將受到每個模塊的位置、引腳布局、I/O 位置、關(guān)鍵路徑、電源和信號分布以及芯片尺寸及其縱橫比的限制。模擬 IP 對這些問題中的大多數(shù)都特別敏感,而模擬模塊也是硬 MAC 的事實使上述所有問題變得復(fù)雜。

一旦放置了芯片的模塊,布線實踐包括首先實現(xiàn)所有關(guān)鍵路徑,無論是模擬還是數(shù)字。然而,當(dāng)涉及非關(guān)鍵路徑時,模擬信號應(yīng)優(yōu)先。此外,無論給定的模擬信號是否至關(guān)重要,所有模擬布線都需要在匹配寄生效應(yīng)、化耦合效應(yīng)和避免過多的 IR 壓降方面進行特殊考慮。它是通過采用模擬信號路由的各種屏蔽技術(shù)、保持走線短、通過直接的路由、差分信號等路由返回信號路徑來實現(xiàn)的。

除了這些在片上集成模擬內(nèi)容的廣泛方法之外,不同類別的模擬電路也可能需要特別注意。DAC 和 ADC 就是一個完美的例子。

使用 DAC 或 ADC 時,除了其分辨率和采樣率之外,還有一些設(shè)計注意事項,即其規(guī)格信噪比 (SNR)、有效位數(shù) (ENOB) 額定值和功耗。遵循奈奎斯特采樣定理(該定理指出,模擬信號的充分?jǐn)?shù)字再現(xiàn)需要以超過模擬 F max的 2 倍的采樣率進行采樣)本身就會給高性能應(yīng)用帶來帶寬、功耗和位同步挑戰(zhàn)。

從采樣的角度來看,無線尤其成問題,而音頻通常對分辨率要求。這就是 ENOB 等參數(shù)具有特殊相關(guān)性的地方。無論給定 DAC 或 ADC 的宣傳分辨率是多少,將此類塊推過其 ENOB 都會降低其 SNR 性能,從而對該塊的真正有用性產(chǎn)生潛在的重大影響。

重要的是,模擬模塊設(shè)計和集成到 SoC 或 ASIC 環(huán)境中根本不像芯片的數(shù)字部分那樣“干凈”和可預(yù)測的工程工作。經(jīng)驗、靈活性和適應(yīng)性是成功的決定因素。