Cause analysis and suppression method of peak current

Time:2022-04-16

Views:2230

Peak current formation:

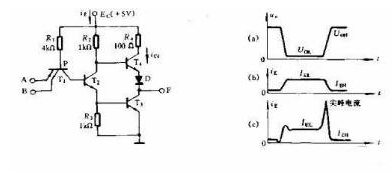

The current IOH pulled from the power supply when the digital circuit outputs high level and the current IOL injected when the digital circuit outputs low level are generally different, that is: IOL "IOH. The TTL NAND gate in the following figure is taken as an example to illustrate the formation of peak current:

Figure 1 TTL NAND gate

The output voltage is shown in figure (a) on the right. Theoretically, the waveform of the power supply current is shown in figure (b) on the right, while the actual power supply current fuse is shown in figure (c) on the right. It can be seen from figure (c) that the power supply current has a short and large peak when the output is converted from low level to high level. The waveform of peak power supply current varies with the type of device used and the capacitive load connected to the output end.

The main causes of peak current are:

The T3 and T4 tubes of the output stage are short and connected at the same time in the design. In the process of NAND gate changing from output low level to high level, the negative jump of input voltage generates a large reverse drive current in the base circuit of T2 and T3. Since the saturation depth of T3 is designed to be greater than T2, the reverse drive current will make T2 out of saturation and cut off first. After T2 is cut off, its collector potential rises to turn on T4. However, T3 is not out of saturation at this time, so in a very short design, T3 and T4 will be turned on at the same time, resulting in a large iC4, making the power supply current form a peak current. R4 in the figure is designed to limit this peak current.

R4 in low-power TTL gate circuit is large, so its peak current is small. When the input voltage changes from low level to high level and the NAND gate output level changes from high to low, T3 and T4 may also be turned on at the same time. However, when T3 starts to turn on, T4 is in the amplified state, and the collector emitter voltage between the two tubes is large, so the peak current generated is small and the impact on the power supply current is relatively small.

Another cause of peak current is the influence of load capacitance. In fact, there is a load capacitor CL at the output of NAND gate. When the output of the gate changes from low to high, the power supply voltage charges the capacitor CL by T4, so a peak current is formed.

When the output of NAND gate changes from high level to low level, capacitor CL discharges through T3. At this time, the discharge current does not pass through the power supply, so the discharge current of CL has no effect on the power supply current.

Suppression method of peak current:

1. Take measures on the wiring of the circuit board to minimize the stray capacitance of the signal line;

2. Another method is to try to reduce the internal resistance of the power supply so that the peak current will not cause excessive power supply voltage fluctuation;

3. The usual method is to use to filter, which is usually placed at the power inlet of the circuit board

A 1uF ~ 10uF filter to filter out low-frequency noise; A 0.01uF ~ 0.1uF (high-frequency filter capacitor) is placed between the power supply and ground of each active device in the circuit board to filter out high-frequency noise. The purpose of filtering is to filter the AC interference superimposed on the power supply, but it is not that the larger the capacitance used, the better, because the actual capacitance is not an ideal capacitance and does not have all the characteristics of an ideal capacitance.

The selection of decoupling capacitance can be calculated according to C = 1 / F, where f is the circuit frequency, i.e. 0.1uF for 10MHz and 0.01uF for 100MHz. Generally, 0.1 ~ 0.01uF can be taken.

The high-frequency filter capacitor placed next to the active device has two functions: one is to filter out the high-frequency interference transmitted along the power supply, and the other is to supplement the peak current required by the device at high speed. Therefore, the placement position of the capacitor needs to be considered.

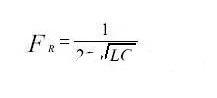

Due to the parasitic parameters, the actual capacitance can be equivalent to the resistance and inductance connected in series on the capacitance, which are called equivalent series resistance (ESR) and equivalent series inductance (ESL). In this way, the actual capacitance is a series resonant circuit, and its resonant frequency is (Fig. 2):

Figure 2 resonant frequency

The actual capacitance is capacitive at frequencies below FR and inductive at frequencies above fr, so the capacitance is more like a band stop filter.

Due to its large ESL and fr less than 1MHz, 10uF electrolytic capacitor has a good filtering effect for low-frequency noise such as 50Hz, but has no effect on hundreds of megabytes of high-frequency switching noise.

The ESR and ESL of the capacitor are determined by the structure of the capacitor and the medium used, not the capacitance. The ability to suppress high-frequency interference cannot be improved by using larger capacitance. For the same type of capacitance, the impedance of large capacitance is smaller than that of small capacitance at a frequency lower than fr, but if the frequency is higher than fr, ESL determines that there will be no difference between the two impedances.

Using too many high-capacity capacitors on the circuit board is not helpful to filter out high-frequency interference, especially when using high-frequency switching power supply. Another problem is that there are too many high-capacity capacitors, which increases the impact on the power supply when powering on and hot plugging the circuit board, which is easy to cause problems such as power supply voltage drop, circuit board connector ignition, slow voltage rise in the circuit board and so on.

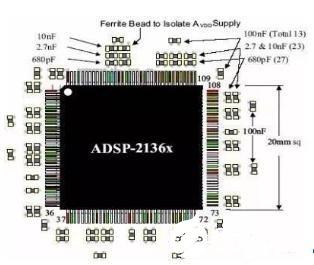

Decoupling capacitor placement during layout

For the installation of capacitors, the first thing to mention is the installation distance. The capacitor with the smallest capacitance has the highest resonant frequency and the smallest decoupling radius, so it is placed closest to the chip. Those with larger capacity can be a little farther away, and the outermost layer is placed with the largest capacity. All capacitors on the chip should be decoupled as close as possible.

Figure 3 below is an example of placement. The capacitance level in this example roughly follows the 10 times level relationship.

Fig. 3 capacitor placement

It should also be noted that when placing, it is best to evenly distribute around the chip, and do this for each capacitance level. Usually, the arrangement position of power and ground pins is considered in the design of the chip, which is generally evenly distributed on the four sides of the chip. Therefore, the voltage disturbance exists around the chip, and the decoupling must be uniform to the whole chip area. If the 680pf capacitors in the figure above are placed on the upper part of the chip, due to the decoupling radius problem, the voltage disturbance at the lower part of the chip cannot be well decoupled.

Installation of capacitor

When installing the capacitor, pull out a small section of outgoing line from the pad, and then connect it with the power plane through the via. The same is true for the grounding terminal. In this way, the current loop flowing through the capacitor is: power plane - "via -" outgoing line - "pad -" capacitor - "pad -" outgoing line - "via -" ground plane. Figure 2 visually shows the current return path.

Figure 4 capacitor installation

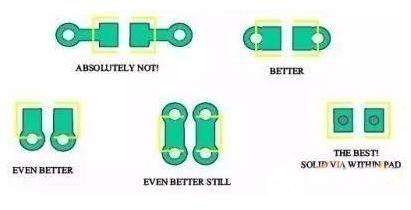

The first method is to lead out a long lead from the pad and then connect the via, which will introduce a large parasitic inductance. This must be avoided. This is the worst installation method.

The second method punches holes at the two end points of the pad close to the pad, which is much smaller than the first method, and the parasitic inductance is also smaller, which is acceptable.

The third method is to punch holes on the side of the pad to further reduce the loop area, and the parasitic inductance is smaller than the second method, which is a better method.

The fourth method is to punch holes on both sides of the pad. Compared with the third method, it is equivalent to that each end of the capacitor is connected to the power plane and ground plane in parallel through holes, which is smaller than the third parasitic inductance. As long as space allows, try to use this method.

The last method is to directly punch holes on the pad with the smallest parasitic inductance, but there may be problems in welding. Whether to use it depends on the processing capacity and mode.

The third and fourth methods are recommended.

It should be emphasized that some engineers sometimes use common vias for multiple capacitors in order to save space. Under no circumstances should they do so. It is best to find a way to optimize the design of capacitor combination and reduce the number of capacitors.

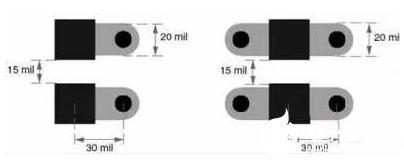

Since the wider the printed line, the smaller the inductance, the outgoing line from the pad to the via shall be widened as much as possible. If possible, it shall be the same as the pad width. In this way, even for 0402 encapsulated capacitors, you can also use 20MIL wide outgoing lines. The installation of outgoing line and through hole is shown in Figure 5. Pay attention to various dimensions in the figure.

Figure 5 installation of outgoing line and through hole

|

Disclaimer: This article is transferred from other platforms and does not represent the views and positions of this site. If there is infringement or objection, please contact us to delete. thank you! |